DS3577-3.4

## MA2909/11

## RADIATION HARD MICROPROGRAM SEQUENCER

The MA2909/11 Microprogram Sequencer is fully compatible with the industry standard 2909A and 2911A components, and forms part of the GPS 2900 Series of devices. The series offers a building block approach to microcomputer and controller design, with each device in the range being expandable to permit efficient emulation of any microcode machine.

The devices have tristate outputs and have an internal address register, with all internal registers changing state on LOW to HIGH clock transition.

The 4-bit slice can cascade to any number of microwords. Branch input for N-way branches is supported. Additional features include:

- 4-bit cascadable microprogram counter.

- 4 x 4 file with stack counter supporting nesting microsubroutines.

- Zero input for returning to the zero microcode word.

- Individual OR input for each bit for branching to higher microinstructions (2909 only).

The 2909 is a 4-bit wide address controller intended for sequencing through a series of microinstructions contained in a ROM or PROM. Two 2909s may be interconnected to generate an 8-bit address (256 words), and three may be used to generate a 12-bit address (4K words).

The 2909 can select an address from any of four sources:

- 1) A set of external direct inputs (D);

- 2) External data from the R inputs, stored in an internal register;

- 3) A four-word push/pop stack; or

- 4) A program counter register (which usually contains the last address plus one).

The push/pop stack includes certain control lines so that it can efficiently execute nested subroutine linkages. Each of the four outputs can be OR'ed with an external input for conditional skip or branch instructions, and a separate line forces the outputs to all zeroes. The outputs are three-state.

The 2911 is an identical circuit to the 2909 except the four OR inputs are removed and the D and R inputs are tied together.

## **FEATURES**

- Fully Compatible with Industry Standard 2909A and 2911A Components

- Radiation Hard CMOS SOS Technology

- High SEU Immunity

- High Speed / Low Power

- Fully TTL Compatible

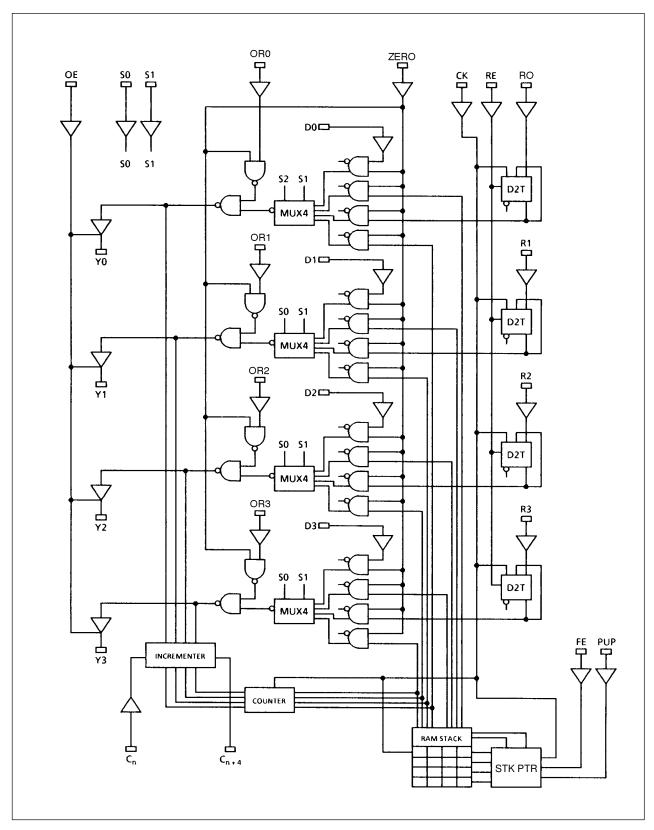

Figure 1: Microprogram Sequencer Block Diagram

The 2909/2911 are CMOS SOS microprogram sequencers intended for use in high-speed microprocessor applications. The device is a cascadable 4-bit slice such that two devices allow addressing of up to 256 words of microprogram and three devices allow addressing of up to 4K words of microprogram. A detailed logic diagram is shown in figure 1.

The device contains a four input multiplexer that is used to select either the address register, direct inputs, microprogram counter, or file as the source of the next microinstruction address. This multiplexer is controlled by the S0 and S1 inputs.

The address register consists of four D-type, edge triggered flip-flops with a common clock enable. When the address register enable is LOW, new data is entered into the register on the clock LOW-to-HIGH transition. The address register is available at the multiplexer as a source for the next microinstruction address The direct input is a 4-bit field of inputs to the multiplexer and can be selected as the next microinstruction address. On the 2911 the direct inputs are also used as inputs to the register. This allows an N-way branch where N is any word in the microcode.

The 2909/2911 contains a microprogram counter (µPC) that is composed of a 4-bit incrementer followed by a 4bit register. The incrementer has carry-in (C<sub>n</sub>) and carry-out (C<sub>n</sub> + 4) such that cascading to larger word lengths is straight forward. The µPC can be used in either of two ways. When the least significant carry-in to the incrementer is HIGH, the microprogram register is loaded on the next clock cycle with the current Y output word plus one  $(Y + 1 \rightarrow \mu PC)$ . Thus sequential microinstructions can be executed. If this least significant C<sub>n</sub> is LOW, the incrementer passes the Y output word unmodified and the microprgram register is loaded with the same Y word on the next clock cycle (Y  $\rightarrow \mu PC$ ). Thus, the same microinstruction can be executed any number of times by using the 4x4 file (stack). The file is used to provide return address linkage when executing microsubroutines. The file contains a built-in stack pointer (SP) which always points to the last file word written. This allows stack reference operations (looping) to be performed without a push or pop.

The stack pointer operates as an up/down counter with separate push/pop and file enable inputs. When the file enable input is LOW and the push/pop input is HIGH, the PUSH operation is enabled. This causes the stack pointer to increment and the file to be written with the required return linkage - the next microinstruction address following the subroutine jump which initiated the PUSH.

If the file enable input is LOW and the push/pop control is LOW, a POP operation occurs. This implies the usage of the return linkage during this cycle and thus a return from subroutine. The next LOW-to-HIGH clock transition causes the stack pointer to decrement. If the file enable is HIGH, no action is taken by the stack pointer regardless of any other input.

The stack pointer linkage is such that any combination of push, pop or stack references can be achieved. One microinstruction subroutine can be performed. Since the stack is 4 words deep, up to four microsubroutines can be nested.

The ZERO input is used to force the four outputs to the binary zero state. When the ZERO input is LOW all Y outputs are LOW regardless of any other inputs (except OE). Each Y output bit also has a separate OR input such that a conditional logic one can be forced at each Y output. This allows jumping to different microinstructions on programmed conditions.

The 2909/2911 feature three-state Y outputs. These can be particularly useful in designs requiring external equipment to provide automatic checkout of the microprocessor. The internal control can be placed in the high impedance state and preprogrammed.

#### **MULTIPLEXER SELECT CODES**

Table 1 lists the select codes for the multiplexer. The two bits applied from the microword register (and additional combinational logic for branching) determine which data source contains the address for the next microinstruction. The contents of the selected source will appear on the Y outputs. Table 1 also shows the truth table for the output control and for the control of the push/pop stack. Table 2 shows in detail the effect of  $S_0$ ,  $S_1$ , FE and PUP on the 2909. These four signals define the address that apears on the Y outputs and what the state of all the internal registers will be following the clock LOW-to-HIGH edge. In this illustration, the microprogram counter is assumed to contain initially some word J, the address register some word K, and the four words in the push/pop stack contain  $R_a$  through  $R_d$ .

| OR1 | ZERO | OE | Y1                                               |

|-----|------|----|--------------------------------------------------|

| Х   | Х    | Н  | Z                                                |

| Х   | L    | L  | L                                                |

| Н   | Н    | L  | Н                                                |

| L   | Н    | L  | Source selected by S <sub>0</sub> S <sub>1</sub> |

H = High, L = Low, Z = High Impedance

Table 1a: Output Control

| FE | ZERO | PUSH-POP stack change               |

|----|------|-------------------------------------|

| Н  | Х    | No change                           |

| L  | Н    | Increment stack pointer, then push  |

|    |      | current PC on to STK0               |

| Ĺ  | Ĺ    | Pop stack (decrement stack pointer) |

H = High, L = Low, X = Irrelevant

Table 1b: Synchronous Stack Control

| S <sub>1</sub> | S <sub>2</sub> | Symbol                   |       |

|----------------|----------------|--------------------------|-------|

| L              | L              | Microprogram counter     | μPC   |

| L              | Н              | Address/Holding register | AR    |

| Н              | L              | Push-Pop stack           | STKO  |

| Н              | Н              | Direct inputs            | $D_1$ |

Table 1c: Address Selection

## MA2909/11

| Cycle               | S1 | S0     | FE | PUP | μРС                     | REG    | STK0                             | STK1                                               | STK2                                               | <b>STK3</b>                      | Y <sub>OUT</sub> | Comment                              | Principal Use       |

|---------------------|----|--------|----|-----|-------------------------|--------|----------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------|------------------|--------------------------------------|---------------------|

| N<br>N + 1          | L  | L _    | L  | L   | J<br>J + 1              | K<br>K | R <sub>a</sub><br>R <sub>b</sub> | R <sub>b</sub>                                     | R <sub>c</sub><br>R <sub>d</sub>                   | R <sub>d</sub><br>R <sub>a</sub> | ٠ ح              | Pop Stack                            | End Loop            |

| N                   | L  | L      | L  | Н   | J                       | K<br>K | Ra                               | R <sub>b</sub>                                     | $R_c$                                              | R <sub>d</sub>                   | J                | Push μPC                             | Set-up Loop         |

| N + 1<br>N<br>N + 1 | L  | L _    | Н  | Х   | J + 1<br>J<br>J + 1     | K<br>K | R <sub>a</sub>                   | R <sub>a</sub><br>R <sub>b</sub><br>R <sub>h</sub> | R <sub>b</sub><br>R <sub>c</sub><br>R <sub>c</sub> | $R_{d}$ $R_{d}$                  | J                | Continue                             | Continue            |

| N<br>N + 1          | L  | Н _    | L  | L   | J<br>K + 1              | K<br>K | R <sub>a</sub><br>R <sub>b</sub> | R <sub>b</sub>                                     | R <sub>c</sub><br>R <sub>d</sub>                   | R <sub>d</sub><br>R <sub>a</sub> | K<br>-           | Pop Stack;<br>Use AR for Address     | End Loop            |

| N<br>N + 1          | L  | H _    | L  | Н   | J<br>K + 1              | K<br>K | R <sub>a</sub>                   | R <sub>b</sub>                                     | R <sub>c</sub>                                     | R <sub>d</sub>                   | K<br>-           | Push μPC;<br>Jump to Address in AR   | JSR AR              |

| N<br>N + 1          | L  | Н -    | Н  | Х   | J<br>K + 1              | K<br>K | R <sub>a</sub><br>R <sub>a</sub> | R <sub>b</sub>                                     | R <sub>c</sub>                                     | R <sub>d</sub><br>R <sub>d</sub> | K<br>-           | Jump to Address in AR                | JMP AR              |

| N<br>N + 1          | Н  | L<br>- | L  | L   | J<br>R <sub>a</sub> + 1 | K<br>K | R <sub>a</sub><br>R <sub>b</sub> | R <sub>b</sub>                                     | R <sub>c</sub><br>R <sub>d</sub>                   | R <sub>d</sub><br>R <sub>a</sub> | R <sub>a</sub>   | Jump to Address in STK0; Pop Stack   | RTS                 |

| N<br>N + 1          | Н  | L<br>- | L  | Н   | J<br>R <sub>a</sub> + 1 | K<br>K | R <sub>a</sub>                   | R <sub>b</sub>                                     | R <sub>c</sub><br>R <sub>b</sub>                   | R <sub>d</sub><br>R <sub>c</sub> | R <sub>a</sub>   | Jump to Address in<br>STK0; Push μPC |                     |

| N<br>N + 1          | Н  | L -    | Н  | Х   | J<br>R <sub>a</sub> + 1 | K<br>K | R <sub>a</sub>                   | R <sub>b</sub>                                     | R <sub>c</sub>                                     | R <sub>d</sub>                   | R <sub>a</sub>   | Jump to Address in STK0              | Stack Ref<br>(Loop) |

| N<br>N + 1          | Н  | H -    | L  | L   | J<br>D + 1              | K<br>K | R <sub>a</sub><br>R <sub>b</sub> | R <sub>b</sub>                                     | R <sub>c</sub><br>R <sub>d</sub>                   | R <sub>d</sub><br>R <sub>a</sub> | D<br>-           | Pop Stack;<br>Jump to Address on D   | End Loop            |

| N<br>N + 1          | Н  | Н _    | L  | Н   | J<br>D+1                | K<br>K | R <sub>a</sub>                   | R <sub>b</sub>                                     | R <sub>c</sub>                                     | R <sub>d</sub><br>R <sub>c</sub> | D<br>-           | Jump to Address on D;<br>Push μPC    | JSR D               |

| N<br>N + 1          | Н  | H -    | Н  | Х   | J<br>D + 1              | K<br>K | R <sub>a</sub>                   | R <sub>b</sub>                                     | R <sub>c</sub>                                     | R <sub>d</sub>                   | D<br>-           | Jump to Address on D                 | JMP D               |

1 = High, 0 = Low, X = Irrelevant, Assume  $C_n = High$

Note: STK0 is the location addressed by the stack pointer

Table 2: Output and Internal Next-Cycle Register States for 2909/2911

Table 3 (Page 5) illustrates the execution of a subroutine using the 2909. The configuration of Figure 2 is assumed. The instruction being executed at any given time is the one contained in the microword register ( $\mu$ WR). The contents of the  $\mu$ WR also control (indirectly, perhaps) the four signals S0, S1, FE, and PUP. The starting address of the subroutine is applied to the D inputs of the 2909 at the appropriate time.

In the column on the left is the sequence of microinstructions to be executed. At address J+2, the sequence control portion of the microinstruction contains the command "Jump to subroutine at A".

At the time  $T_2$ , this instruction is in the  $\mu WR$ , and the 2909 inputs are set-up to execute the jump and save the return address. The subroutine address A is applied to the D inputs from the  $\mu WR$  and appears on the Y outputs. The first instruction of the subroutine, I(A), is accessed and is at the inputs of the  $\mu WR$ . On the next clock transition, I(A) is loaded into the  $\mu WR$  for execution, and the return address J + 3 is pushed on to the stack. The return instruction is executed at  $T_5$ . Table 4 is a similar timing chart showing one subroutine linking to a second, the latter consisting of only one microinstruction.

| Execute Cycle                                |                                 | T <sub>0</sub> | T <sub>1</sub> | T <sub>2</sub> | <b>T</b> <sub>3</sub> | <b>T</b> <sub>4</sub> | <b>T</b> <sub>5</sub> | <b>T</b> <sub>6</sub> | <b>T</b> <sub>7</sub> | T <sub>8</sub> | T <sub>9</sub> |

|----------------------------------------------|---------------------------------|----------------|----------------|----------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|----------------|

|                                              | S <sub>1</sub> , S <sub>0</sub> | 0              | 0              | 3              | 0                     | 0                     | 2                     | 0                     | 0                     |                |                |

| 2909 inputs                                  | FE                              | Н              | Н              | L              | Н                     | Н                     | L                     | Н                     | Н                     |                |                |

| (from µWR)                                   | PUP                             | Х              | Χ              | Н              | Х                     | Х                     | L                     | Х                     | Χ                     |                |                |

|                                              | D                               | Х              | Χ              | Α              | Х                     | Х                     | Χ                     | Х                     | Χ                     |                |                |

|                                              | μPC                             | J + 1          | J + 2          | J + 3          | A + 1                 | A + 2                 | A + 3                 | J + 4                 | J + 5                 |                |                |

|                                              | STK0                            | -              | -              | -              | J + 3                 | J + 3                 | J + 3                 | -                     | -                     |                |                |

| Internal                                     | STK1                            | -              | -              | -              | -                     | -                     | -                     | -                     | -                     |                |                |

| Registers                                    | STK2                            | -              | -              | -              | -                     | -                     | -                     | -                     | -                     |                |                |

|                                              | STK3                            | -              | -              | -              | -                     | -                     | -                     | -                     | -                     |                |                |

| 2909 Output                                  | Υ                               | J + 1          | J + 2          | Α              | A + 1                 | A + 2                 | J + 3                 | J + 4                 | J + 5                 |                |                |

| ROM Output                                   | (Y)                             | I(J + 1)       | JSR A          | I(A)           | I(A + 1)              | RTS                   | I(J + 3)              | I(J + 4)              | I(J + 5)              |                |                |

| Contents of µWR (instruction being executed) | μWR                             | I(J)           | I(J + 1)       | JSR A          | I(A)                  | I(A + 1)              | RTS                   | I(J + 3)              | I(J + 4)              |                |                |

Table 3: Subroutine Execution

## **CONTROL MEMORY**

|                  | Microprogram |                          |  |  |  |  |  |

|------------------|--------------|--------------------------|--|--|--|--|--|

| Execute<br>Cycle | Address      | Sequencer<br>Instruction |  |  |  |  |  |

|                  | J - 1        | -                        |  |  |  |  |  |

| $T_0$            | J            | -                        |  |  |  |  |  |

| T <sub>1</sub>   | J + 1        | -                        |  |  |  |  |  |

| $T_2$            | J + 2        | JSR A                    |  |  |  |  |  |

| $T_6$            | J + 3        | -                        |  |  |  |  |  |

| $T_7$            | J + 4        | -                        |  |  |  |  |  |

|                  | -            | -                        |  |  |  |  |  |

|                  | -            | -                        |  |  |  |  |  |

|                  | -            | -                        |  |  |  |  |  |

|                  | -            | -                        |  |  |  |  |  |

|                  | -            | -                        |  |  |  |  |  |

| $T_3$            | Α            | I(A)                     |  |  |  |  |  |

| $T_4$            | A + 1        | -                        |  |  |  |  |  |

| $T_{5}$          | A + 2        | RTS                      |  |  |  |  |  |

|                  | -            | -                        |  |  |  |  |  |

|                  | -            | -                        |  |  |  |  |  |

|                  | -            | -                        |  |  |  |  |  |

|                  | -            | -                        |  |  |  |  |  |

|                  | -            | -                        |  |  |  |  |  |

|                  | -            | -                        |  |  |  |  |  |

## MA2909/11

| Execute Cycle                                |                                 | T <sub>0</sub> | T <sub>1</sub> | T <sub>2</sub> | <b>T</b> <sub>3</sub> | <b>T</b> <sub>4</sub> | <b>T</b> <sub>5</sub> | <b>T</b> <sub>6</sub> | <b>T</b> <sub>7</sub> | T <sub>8</sub> | T <sub>9</sub> |

|----------------------------------------------|---------------------------------|----------------|----------------|----------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|----------------|

|                                              | S <sub>1</sub> , S <sub>0</sub> | 0              | 0              | 3              | 0                     | 0                     | 2                     | 0                     | 0                     | 2              | 0              |

| 2909 inputs                                  | FE                              | Н              | Н              | L              | Н                     | Н                     | L                     | Н                     | Н                     | L              | Н              |

| (from µWR)                                   | PUP                             | Х              | Χ              | Н              | Х                     | Х                     | L                     | Х                     | Χ                     | L              | Χ              |

|                                              | D                               | Х              | Χ              | Α              | Х                     | Х                     | Х                     | Х                     | Χ                     | Х              | Χ              |

|                                              | μPC                             | J + 1          | J + 2          | J + 3          | A + 1                 | A + 2                 | A + 3                 | B + 1                 | A + 4                 | A + 5          | J + 4          |

|                                              | STK0                            | -              | -              | -              | J + 3                 | J + 3                 | J + 3                 | A + 3                 | J + 3                 | J + 3          | -              |

| Internal                                     | STK1                            | -              | -              | -              | -                     | -                     | -                     | J + 3                 | -                     | -              | -              |

| Registers                                    | STK2                            | -              | -              | -              | -                     | -                     | -                     | -                     | -                     | -              | -              |

| _                                            | STK3                            | -              | -              | -              | -                     | -                     | -                     | -                     | -                     | -              | -              |

| 2909 Output                                  | Υ                               | J + 1          | J + 2          | Α              | A + 1                 | A + 2                 | В                     | A+ 3                  | A + 4                 | J + 3          | J + 4          |

| ROM Output                                   | (Y)                             | I(J + 1)       | JSR A          | I(A)           | I(A + 1)              | JSR B                 | RTS                   | I(A + 3)              | RTS                   | I(J + 3)       | I(J + 4)       |

| Contents of µWR (instruction being executed) | μWR                             | I(J)           | I(J + 1)       | JSR A          | I(A)                  | I(A + 1)              | JRS B                 | RTS                   | I(A + 3)              | RTS            | I(J + 3)       |

Table 4: Two Nested Subroutines

## **CONTROL MEMORY**

|                  | Microp  | orogram                  |

|------------------|---------|--------------------------|

| Execute<br>Cycle | Address | Sequencer<br>Instruction |

|                  | J - 1   | -                        |

| $T_o$            | J       | -                        |

| T <sub>1</sub>   | J + 1   | -                        |

| T <sub>2</sub>   | J + 2   | JSR A                    |

| T <sub>9</sub>   | J + 3   | -                        |

|                  | -       | -                        |

|                  | -       | -                        |

|                  | -       | -                        |

|                  | -       | -                        |

| $T_3$            | Α       | -                        |

| $T_4$            | A + 1   | -                        |

| $T_{5}$          | A + 2   | JSR B                    |

| $T_7$            | A + 3   | -                        |

| T <sub>8</sub>   | A + 4   | RTS                      |

|                  | -       | -                        |

|                  | -       | -                        |

|                  | -       | -                        |

|                  | -       | -                        |

| $T_6$            | В       | RTS                      |

|                  | -       | -                        |

## DC CHARACTERISTICS AND RATINGS

| Parameter               | Min  | Max                  | Units |

|-------------------------|------|----------------------|-------|

| Supply Voltage          | -0.5 | 7                    | V     |

| Input Voltage           | -0.3 | V <sub>DD</sub> +0.3 | V     |

| Current Through Any Pin | -    | 20                   | mA    |

| Operating Temperature   | -55  | 125                  | °C    |

| Storage Temperature     | -65  | 150                  | °C    |

Table 5: Absolute Maximum Ratings

**Note:** Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions, or at any other condition above those indicated in the operations section of this specification, is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Subgroup | Definition                                                          |

|----------|---------------------------------------------------------------------|

| 1        | Static characteristics specified in Table 7 at +25°C                |

| 2        | Static characteristics specified in Table 7 at +125°C               |

| 3        | Static characteristics specified in Table 7 at -55°C                |

| 7        | Functional characteristics at +25°C                                 |

| 8a       | Functional characteristics at +125°C                                |

| 8b       | Functional characteristics at -55°C                                 |

| 9        | Switching characteristics specified in Tables 8, 9 and 10 at +25°C  |

| 10       | Switching characteristics specified in Tables 8, 9 and 10 at +125°C |

| 11       | Switching characteristics specified in Tables 8, 9 and 10 at -55°C  |

Table 6: Definition of Subgroups

| Symbol           | Parameter                 | Conditions                                                                  | Min.                 | Max. | Units |

|------------------|---------------------------|-----------------------------------------------------------------------------|----------------------|------|-------|

| V <sub>OH</sub>  | Output high voltage       | $V_{DD} = Min., I_{OH} = -2.6mA, V_{IN} = V_{IH} \text{ or } V_{IL}$        | V <sub>DD</sub> -0.5 | -    | V     |

| $V_{OL}$         | Output low voltage        | $V_{DD} = Max., I_{OL} = 16 \text{ mA}, V_{IN} = V_{IH} \text{ or } V_{IL}$ | -                    | 0.5  | V     |

| V <sub>IH</sub>  | Input high level (Note 1) | Guaranteed input logical high voltage for all inputs                        | $V_{DD}/2$           | -    | V     |

| V <sub>IL</sub>  | Input low level (Note 1)  | Guaranteed input logical low voltage for all inputs                         | -                    | 8.0  | V     |

| I <sub>IH</sub>  | Input high current        | $V_{IN} = V_{DD}$ (Note 3)                                                  | -                    | 10   | μΑ    |

| I <sub>IL</sub>  | Input low current         | $V_{IN} = V_{SS}$ (Note 3)                                                  | -                    | -10  | μΑ    |

| I <sub>OZH</sub> | Tristate high current     | $V_O = V_{DD}$ (Note 3)                                                     | -                    | 50   | μΑ    |

| I <sub>OZL</sub> | Tristate low current      | $V_O = V_{SS}$ (Note 3)                                                     | -                    | -50  | μΑ    |

| I <sub>DD</sub>  | Power supply current      |                                                                             | -                    | 10   | mA    |

#### NOTES:

Mil-Std-883, Method 5005, Subgroups 1, 2, 3.

- 1. These input levels provide no guaranteed noise immunity and should only be static tested in a noise-free environment.

- 2.  $V_{DD} = 5V \pm 10\%$ , over full operating temperature range.

- 3. Guaranteed but not tested at low temperatures.

Table 7: DC Operating Characteristics

## MA2909/11

| Time                    |    |

|-------------------------|----|

| Minimum clock low time  | 15 |

| Minimum clock high time | 15 |

Table 8: Cycle Time and Clock Charcteristics

| From input                                | Y  | C <sub>n</sub> + 4 |

|-------------------------------------------|----|--------------------|

| D <sub>1</sub>                            | 35 | 40                 |

| S <sub>0</sub> , S <sub>1</sub>           | 30 | 35                 |

| OR <sub>I</sub>                           | 20 | 30                 |

| $C_n$                                     | -  | 25                 |

| ZERO                                      | 35 | 40                 |

| OE LOW (enable) (Note 2)                  | 25 | -                  |

| OE HIGH (disable) (Note 3)                | 25 | -                  |

| Clock: S <sub>1</sub> S <sub>0</sub> = LH | 40 | 45                 |

| Clock: $S_1S_0 = LL$                      | 40 | 45                 |

| Clock: $S_1S_0 = HL$                      | 50 | 45                 |

| From input                      | Set-up time | Hold Time |  |

|---------------------------------|-------------|-----------|--|

| RE                              | 10          | 10        |  |

| R <sub>I</sub>                  | 10          | 7         |  |

| PUP                             | 20          | 5         |  |

| FE                              | 20          | 10        |  |

| C <sub>n</sub>                  | 15          | 5         |  |

| $D_l$                           | 20          | 0         |  |

| OR <sub>I</sub>                 | 20          | 0         |  |

| S <sub>0</sub> , S <sub>1</sub> | 20          | 0         |  |

| ZERO                            | 25          | 0         |  |

Table 10: Guaranteed Set-up and Hold Times (all in ns)

## Notes:

- 1. CL < 50pF

- 2.  $RL \ge 680\Omega$

- 3. RL  $\geq$  680  $\!\Omega,$  measured 0.5V change in output level

Table 9: Maximum Combinational Propogation Delays

All times in ns across full voltage and temperature range. MIL-STD-883, method 5005, subgroups 9, 10 and 11.

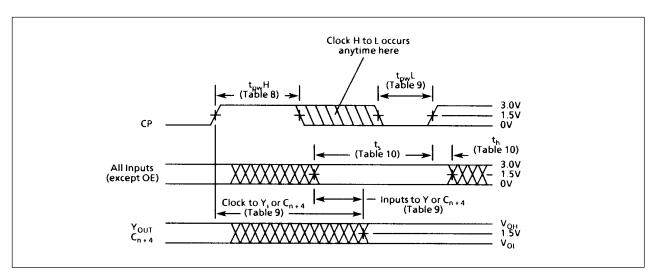

Figure 2

## **PACKAGE OUTLINES**

| Def | Millimetres |            |          | Inches   |            | 1                           |                 |                                                     |

|-----|-------------|------------|----------|----------|------------|-----------------------------|-----------------|-----------------------------------------------------|

| Ref | Min.        | Nom.       | Max.     | Min.     | Nom.       | Max.                        |                 |                                                     |

| Α   | -           | -          | 5.715    | -        | -          | 0.225                       |                 |                                                     |

| A1  | 0.38        | -          | 1.53     | 0.015    | -          | 0.060                       |                 |                                                     |

| b   | 0.35        | -          | 0.59     | 0.014    | -          | 0.023                       |                 |                                                     |

| С   | 0.20        | -          | 0.36     | 0.008    | -          | 0.014                       |                 |                                                     |

| D   | -           | -          | 36.02    | -        | -          | 1.418                       |                 |                                                     |

| е   | -           | 2.54 Typ.  | -        | -        | 0.100 Typ. | -                           |                 |                                                     |

| e1  | -           | 15.24 Typ. | -        | -        | 0.600 Typ. | -                           |                 |                                                     |

| Н   | 4.71        | -          | 5.38     | 0.185    | -          | 0.212                       |                 |                                                     |

| Ме  | -           | -          | 15.90    | -        | -          | 0.626                       | ]               |                                                     |

| Z   | -           | -          | 1.27     | -        | -          | 0.050                       |                 |                                                     |

| W   | -           | -          | 1.53     | -        | -          | 0.060                       |                 |                                                     |

|     | 14          |            |          | 28<br>W— |            | D3 OR2 D2 OR1 D1 OR0 D0 GND | 8 9 10 11 12 13 | 22 OEN 21 Y3 20 Y2 19 Y1 18 Y0 17 S1 16 S0 15 ZERON |

| _   | -           |            | <u> </u> | ı        | Seating F  | Plane —                     |                 | M <sub>E</sub>                                      |

Figure 3: 28-Lead Ceramic DIL (Solder Seal) - Package Style C

|     | Millimetres |      |       | Inches |      |       |           |  |

|-----|-------------|------|-------|--------|------|-------|-----------|--|

| Ref | Min.        | Nom. | Max.  | Min.   | Nom. | Max.  | ı         |  |

| Α   | -           | -    | 2.97  | -      | -    | 0.117 | ı         |  |

| b   | 0.381       | -    | 0.482 | 0.015  | -    | 0.019 | ı         |  |

| С   | 0.076       | -    | 0.152 | 0.003  | -    | 0.006 | ı         |  |

| D   | 18.08       | -    | 18.49 | 0.712  | -    | 0.728 | ı         |  |

| E   | 12.50       | -    | 12.9  | 0.492  | -    | 0.508 | ı         |  |

| E2  | 9.45        | -    | 9.85  | 0.372  | -    | 0.388 | ı         |  |

| е   | 1.143       | -    | 1.40  | 0.045  | -    | 0.055 | İ         |  |

| L   | 8.00        | -    | 9.27  | 0.315  | -    | 0.365 | ı         |  |

| Q   | 0.66        | -    | -     | 0.026  | -    | -     | ı         |  |

| S   | -           | -    | 1.14  | -      | -    | 0.045 | ı         |  |

|     |             |      |       |        |      |       | <b>—</b>  |  |

| -   |             |      | •     |        |      |       | e A A Q Q |  |

Figure 3: 28-Lead Dual Flatpack (Solder Seal) - Package Style C

#### RADIATION TOLERANCE

## **Total Dose Radiation Testing**

For product procured to guaranteed total dose radiation levels, each wafer lot will be approved when all sample devices from each lot pass the total dose radiation test.

The sample devices will be subjected to the total dose radiation level (Cobalt-60 Source), defined by the ordering code, and must continue to meet the electrical parameters specified in the data sheet. Electrical tests, pre and post irradiation, will be read and recorded.

GEC Plessey Semiconductors can provide radiation testing compliant with MIL-STD-883 test method 1019, lonizing Radiation (Total Dose).

| Total Dose (Function to specification)*      | 3x10 <sup>5</sup> Rad(Si)             |

|----------------------------------------------|---------------------------------------|

| Transient Upset (Stored data loss)           | 5x10 <sup>10</sup> Rad(Si)/sec        |

| Transient Upset (Survivability)              | >1x10 <sup>12</sup> Rad(Si)/sec       |

| Neutron Hardness (Function to specification) | >1x10 <sup>15</sup> n/cm <sup>2</sup> |

| Single Event Upset**                         | 1x10 <sup>-10</sup> Errors/bit day    |

| Latch Up                                     | Not possible                          |

<sup>\*</sup> Other total dose radiation levels available on request

Table 11: Radiation Hardness Parameters

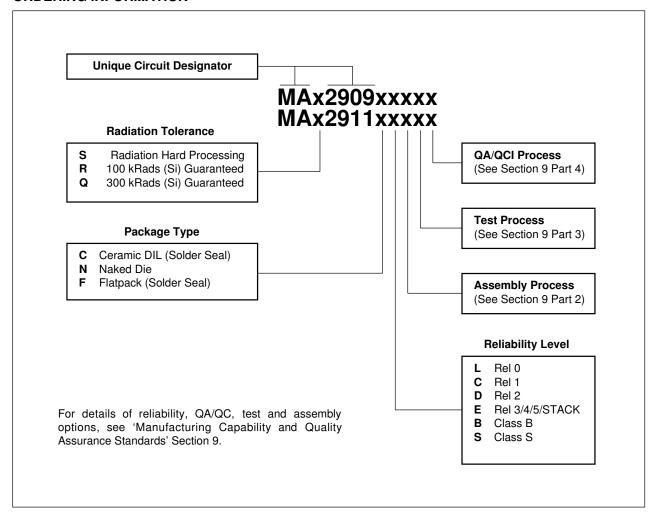

## ORDERING INFORMATION

<sup>\*\*</sup> Worst case galactic cosmic ray upset - interplanetary/high altitude orbit

**HEADQUARTERS OPERATIONS**

#### **GEC PLESSEY SEMICONDUCTORS**

Cheney Manor, Swindon,

Wiltshire, SN2 2QW, United Kingdom.

Tel: (01793) 518000 Fax: (01793) 518411

## **GEC PLESSEY SEMICONDUCTORS**

P.O. Box 660017,

1500 Green Hills Road, Scotts Valley, California 95067-0017,

United States of America. Tel: (408) 438 2900 Fax: (408) 438 5576

#### **CUSTOMER SERVICE CENTRES**

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax: (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510

- NORTH AMERICA Scotts Valley, USA Tel: (408) 438 2900 Fax: (408) 438 7023

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

- SWEDEN Stockholm Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- TAIWAN, ROC Taipei Tel: 886 2 5461260 Fax: 886 2 7190260

- UK, EIRE, DENMARK, FINLAND & NORWAY Swindon, UK

Tel: (01793) 518527/518566 Fax: (01793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1995 Publication No. DS3577-3.3 March 1995

TECHNICAL DOCUMENTATION - NOT FOR RESALE. PRINTED IN UNITED KINGDOM.

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior knowledge the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

# For more information about all Zarlink products visit our Web Site at

www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink s  $I^2C$  components conveys a licence under the Philips  $I^2C$  Patent rights to use these components in and  $I^2C$  System, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

Zarlink and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2001, Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE